Тема урока: Шифраторы и дешифраторы. Назначение, структура, применение

Дешифраторы и шифраторы (также, как и элементы И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ) являются комбинационными элементами: потенциалы на их выходах зависят от сиюминутного состояния входов, с их изменением меняется и ситуация на выходах; такие элементы не сохраняют предыдущее состояние после смены потенциалов на входах, т.е. не обладают памятью.

Дешифраторы могут быть полными и неполными. Полные дешифраторы реагируют на все входные коды, неполные – на коды, величина которых не превосходит некоторого заранее установленного значения. Выходы дешифраторов могут быть прямыми и ин-версными.

Шифраторы выпускаются приоритетными и не приоритетными. У приоритетного шифратора входы имеют разный приоритет. Возбужденный вход с большим приоритетом подавляет действие прежде возбужденного и устанавливает на выходах код, соответ-ствующий своему значению..

Знание материала, излагаемого в данной теме, дадут студенту возможность правильного выбора дешифраторов и шифраторов в зависимости от требуемой разрядности, необходимости использования управляющих входов этих элементов и категории выходов. Он научится организовывать структуры с большим числом входов на маловходовых элементах, а также осуществлять адресацию устройств кодами, разрядность которых превосходит разрядность используемых элементов.

Структура дешифратора.

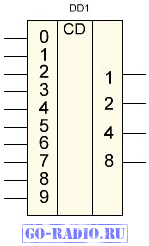

Каждому цифровому коду на входах дешифратора (рис. 3.2, а, б) соответствует логиче-ская 1 (или логический 0) на соответствующем выходе. Иными словами, каждый входной код адресует соответствующий выход, который при этом возбуждается. Поэтому входы дешифратора часто называют адресными. Стоящие возле них цифры (1,2,4…) показывают как соотносятся веса разрядов поступающего двоичного числа.

Выходы дешифратора оцифрованы десятичными числами. Возбуждается тот выход, но-мер которого равен весу входного кода, разряды которого имеют обозначенные веса, т.е. дешифратор расшифровывает (дешифрирует) число, записанное в двоичном коде, представляя его логической 1 (логическим 0) на соответствующем выходе. Так, выход 5 возбуждается при входном коде 101, выход 6 – при входном коде 110 и т.д. Удобно представлять, что выход дешифратора отображает возбудивший его входной код.

Вход V является входом разрешения работы. Если он инверсный (обозначен кружком) , то для функционирования дешифратора на нем должен быть лог. 0 (достаточно этот вход соединить с общим проводом – “землей”). Прямой вход V через резистор соединяется с источником питания. Наличие входа разрешения расширяет функциональные возможности микросхемы.

Дешифратор выбирается так, чтобы число его входов соответствовало разрядности по-ступающих двоичных кодов. Число его выходов равно количеству различных кодов этой разрядности. Так как каждый разряд двоичного кода принимает два значения, то полное количество n-разрядных комбинаций (n-разрядных двоичных кодов) равно 2n. Такое число выходов имеет полный дешифратор.

Неполный дешифратор выбирается, когда некоторые значения адресных кодов не отра-жают физической реальности. Так, например, дешифратор, предназначенный для фикса-ции двоичных кодов десятичного разряда (в нем могут быть цифры 0,1,2…9), должен иметь четыре входа (910 отображается как 10012). Однако комбинации, большие 10012 отображают не цифру, а число, и поэтому (хотя и могут появляться на входах) не должны фиксироваться на выходах, число которых может не превышать десяти.

Основу структуры дешифратора могут составлять элементы И; выход каждого из них является выходом дешифратора. Если этот выход должен быть возбужден, то на входах элемента И должны собираться логические единицы. При этом разряды входного кода, в которых присутствуют логические единицы, должны поступать на входы элемента И не-посредственно, а нулевые разряды должны инвертироваться.

Дешифраторы и шифраторы существуют:

с прямыми входами

с инверсными входами

неполные

неприоритетные

приоритеные

Некоторые типы дешифраторов имеют инверсные выходы: на возбужденном (активизированном) выходе присутствует логиче-ский 0, в то время как на всех других – логические 1. Такие дешифраторы удобно использовать, когда активным сигналом для вы-бора (ввода в действие, инициализации) устройства с выхода дешифратора является логический 0.

Расширение разрядности дешифратора

Общий случай расширения разрядности дешифраторов иллюстрирует рис.3.4. Левый (по схеме) дешифратор постоянно активизирован логической 1 на входе V. Кодами на его ад-ресных входах может быть активизирован (выбран) любой из дешифраторов DC0…DC15. Выбор одного из выходов 0…15 каждого из них определяется кодом на объединенных входах 1, 2, 4, 8. Таким образом, любой из 256 (28) выходов может быть активизирован восьмиразрядным кодом, четыре разряда которого выбирают номер дешифратора, а четы-ре – номер его выхода.

Применение дешифраторов

Основное назначение дешифратора состоит в том, чтобы выбрать (адресо-вать, инициализировать) один объект из множества находящихся в устройстве. Рис. 3.5 иллюстрирует это применение. Каждому объекту присваивают определенный адрес (номер). Когда на входы дешифратора поступает двоичный код адреса, соответствующий элемент активизируется за счет появления логического 0 на связанном с ним выходе де-шифратора, а остальные элементы ос-таются заблокированными.

Можно предусмотреть, чтобы с одного из выходов дешифратора на определенный блок поступал управляющий сигнал, когда на входах дешифратора появляется определенный код, соответствующий, например, превышению какого-либо параметра (температуры, напряжения и т.д.), который должен быть приведен к нормальному уровню указанным блоком.

Когда число адресуемых устройств невелико, многие выходы дешифратора остаются неза-действованными. При этом может оказаться целесообразным (в частности, по экономическим соображениям) использовать не микросхему дешифратора, а реализовать ее фрагмент логическими элементами.

На дешифраторе могут быть реализованы логические функции. Пусть, к примеру, y = />3 x2 />1 + />3 x2 x 1 + x3 />2 x 1. Логические переменные подаются на адресные входы дешифратора. Первая конъюнкция (ее вес равен 2) возбуждает выход №2, вторая – выход №3, третья – выход №5. Так как условие y = 1 должно иметь место при наличии любой из этих конъюнкций, то выходы 2, 3 и 5 надо объединить дизъюнкцией.

Шифраторы

Структура шифратора.

Шифратор решает задачу, обратную дешифратору: в частности, на его выходах устанавливается двоичный код, соответствующий десятичному номеру возбужденного информационного входа.

При построении шифратора для получения на выходе натурального двоичного кода учитывают, что единицу в младшем разряде такого кода имеют нечетные десятичные цифры 1, 3, 5, 7,…, т. е. на выходе младшего разряда должна быть 1, если она есть на входе № 1 или на входе № 3 и т. д. Поэтому входы под указанными номерами через элемент ИЛИ соединяются с выходом младшего разряда. Единицу во втором разряде двоичного кода имеют десятичные цифры 2, 3, 6, 7,.. .; входы с этими номерами через элемент ИЛИ должны подключаться к выходу шифратора, на котором устанавливается второй разряд кода. Аналогич-но, входы 4, 5, 6, 7,… через элемент ИЛИ должны быть соединены с выходом, на котором устанавливается третий разряд, так как их коды имеют в этом разряде единицу, и т. д.

Возможно построение схемы шифратора, где E – вход разрешения работы, а Е0– выход, логический 0 на котором свидетельствует о том, что ни один информационный вход не возбужден. Для расширения разрядности (каскадирования) шифраторов вход E последующего шифратора соединяют с выходом E0.предыдущего. Если информационные входы предыдущего шифратора не возбуждены (E0=0), то последующий шифратор получает разрешение работать.

Назначение и применение шифраторов и дешифраторов

Шифратор может быть организован не только для представления (кодирования) десятичного числа двоичным кодом, но и для выдачи определенного кода (его значение заранее выбирается), например, при нажатии клавиши с соответствующим символом. При появлении этого кода система оповещается о том, что нажата определенная клавиша клавиатуры.

Шифраторы применяются в устройствах, преобразующих один вид кода в другой. При этом вначале дешифрируется комбинация исходного кода, в результате чего на соответствующем выходе дешифратора появляется логическая 1. Это отображение входного кода, значение которого определено номером возбужденного выхода дешифратора, подается на шифратор, организованный с таким расчетом, чтобы каждый входной код вызывал появление заданного выходного кода

Одними из очень важных элементов цифровой техники, а особенно в компьютерах и системах управления являются шифраторы и дешифраторы. Когда мы слышим слово шифратор или дешифратор, то в голову приходят фразы из шпионских фильмов. Что- то вроде: расшифруйте депешу и зашифруйте ответ. В этом нет ничего неправильного, так как в шифровальных машинах наших и зарубежных резидентур используются шифраторы и дешифраторы.

Шифраторы.

Таким образом, шифратор (кодер), это электронное устройство, в данном случае микросхема, которая преобразует код одной системы счисления в код другой системы. Наибольшее распространение в электронике получили шифраторы, преобразующие позиционный десятичный код, в параллельный двоичный. Вот так шифратор может обозначаться на принципиальной схеме.

К примеру, представим, что мы держим в руках обыкновенный калькулятор, которым сейчас пользуется любой школьник.

Поскольку все действия в калькуляторе выполняются с двоичными числами (вспомним основы цифровой электроники), то после клавиатуры стоит шифратор, который преобразует вводимые числа в двоичную форму.

Поскольку все действия в калькуляторе выполняются с двоичными числами (вспомним основы цифровой электроники), то после клавиатуры стоит шифратор, который преобразует вводимые числа в двоичную форму.

Все кнопки калькулятора соединяются с общим проводом и, нажав, к примеру, кнопку 5 на входе шифратора, мы тут же получим двоичную форму данного числа на его выходе.

Конечно же, шифратор калькулятора имеет большее число входов, так как помимо цифр в него нужно ввести ещё какие-то символы арифметических действий, поэтому с выходов шифратора снимаются не только числа в двоичной форме, но и команды.

Если рассмотреть внутреннюю структуру шифратора, то несложно убедиться, что он выполнен на простейших базовых логических элементах.

Во всех устройствах управления, которые работают на двоичной логике, но для удобства оператора имеют десятичную клавиатуру, используются шифраторы.

бразования будет рассмотрен в третьей части учебника.

Вопросы для самоконтроля

Что такое дешифратор?

Как обозначается линейный дешифратор?

Объяснить принцип работы демультиплексора

Что такое шифратор?

Где используют шифраторы?

Что такое мультиплексор?

Достоинства цифровых систем шифрации и дешифрации команд в аппаратуре дистанционного управления моделями уже были отмечены в литературе. Ниже описан еще один вариант комплекса шифратор-дешифратор на 15 дискретных команд, предназначенный для той же цели.

Схема шифратора изображена на рис. 1, а дешифратора - на рис. 2. Форма сигнала в некоторых характерных точках устройства показана на рис. 3.

На выходе шифратора команд действуют пачки импульсов отрицательной полярности (график 4 на рис. 3).

Частота повторения пачек импульсов равна f/32, где f - частота задающего генератора, выполненного на логических элементах DD1.1.DD1.2 (рис. I) по схеме симметричного мультивибратора.

С задающего генератора импульсы (график 1) поступают на счетчик DD2 и на элемент совпадения.DD4.1. Импульсы частотой f через этот элемент будут проходить тогда, когда триггеры DD3 и DD1.3.DD1.4 находятся в единичном состоянии (графики 2 и 3). Счетный триггер DD3 переключается после каждого 16-го импульса, поступающего на счетчик DD2. Свободные входы триггера DD3 объединены и подключены через резистор сопротивлением 1 кОм к плюсовому выводу источника питания. RS-триггер DD1.3.DD1.4 устанавливается в единичное состояние по нулевому уровню сигнала на выходе 0 (вывод 1) дешифратора DD5 и в нулевое состояние - по нулевому уровню сигнала на том из выходов дешифратора, который подключен к выводу 2 элемента DD1.4 через контакты одной из кнопок SB I-SB 15.

Число импульсов в пачке равно номеру нажатой кнопки. Если не нажата ни одна из кнопок, то шифратор вырабатывает пачки по 16 импульсов, так как RS-триггер DD1.3.DD1.4 не переводится в нулевое состояние.

Дешифратор команд собран на четы-рех микросхемах (рис. 2). Узел, собранный на элементах DD1.2.DD1.3. представляет собой селектор импульсов. За время между двумя импульсами отрицательной полярности частотой f конденсатор С1 не успевает зарядиться до напряжения, достаточного для того, чтобы перевести элемент DD1.2 в нулевое состояние, и на выходе элемента DD1.3 сохраняется уровень-сигнала, соответствующий логическому 0. В течение же промежутка времени между пачками импульсов конденсатор С1 заряжается до единичного напряжения на выводе 2 элемента DD1.2 (график 5) и на выходе элемента DD1.3 появляется сигнал 1 (график 6). Диод VDI обеспечивает быструю разрядку конденсатора С1.

По спаду импульсов с выхода элемента DD1.3 счетчик DD2 устанавливается в нулевое состояние, а из их фронтов дифференцирующая цепь C3.R4 формирует импульсы записи информации со счетчика DD2 в запоминающий узел на триггере DD3. При одном импульсе в пачке счетчик DD2 остается в нулевом состоянии, при двух он переходит в состояние 1, при трех - в состояние 2 и т. д.

К выходам дешифратора DD4 через промежуточное звено - электронное реле - подключают исполнительные устройства. Схема электронного реле изображена на рис. 4. Первое электронное реле подключают к выходу О (вывод 1) дешифратора DD4, второе - к выходу 1 и т. д. Шестнадцатое реле, подключенное к выводу 17, включено тогда, когда в шифраторе не нажата ни одна из кнопок. При таком построении приемника может быть включенным одновременно только одно исполнительное устройство. Оно включается на время нажатия кнопки в шифраторе команд в передатчике.

Для независимого включения и выключения исполнительных устройств независимо между дешифратором и каждым электронным реле надо включить RS-трнггер по схеме рис. 5. Входы триггеров присоединяют к двум соседним выходам дешифратора; например, входы S и R первого триггера подключают к выходам 0 и 1 дешифратора соответственно, второго - к выходам 2 и 3, третьего - к выходам 4 и 5 и т. д. Число исполнительных устройств при этом уменьшается вдвое. Конденсатор С1 необходим для установки RS-триггера в единичное состояние при включении питания.

Когда на выходе RS-триггера сигнал высокого уровня, то реле К1 обесточено. Если на некоторое время на вход R подать сигнал 0, триггер установится в нулевое состояние и реле К1 включится. Реле выключится тогда, когда нулевой уровень сигнала будет подан на некоторое время на вход S. Таким образом, команда по одному из каналов включает реле, а по соседнему - выключает. При необходимости часть электронных реле может быть включена по схеме рис. 4, а остальные - с RS-триггером. Реле К1 - РЭС15, паспорт РС4.591.003.

При проверке работоспособности устройства выход шифратора команд соединяют со входом дешифратора. Частота задающего генератора может быть выбрана другой, нужно только подобрать конденсатор С1 в дешифраторе команд (при большей частоте емкость конденсатора должна быть меньше). К стабильности частоты задающего генератора высоких требований не предъявляется.

Шифратор решает задачу, обратную дешифратору: в частности, на его выходах устанавливается двоичный код, соответствующий десятичному номеру возбужденного информационного входа.

При построении шифратора для получения на выходе натурального двоичного кода учитывают, что единицу в младшем разряде такого кода имеют нечетные десятичные цифры 1, 3, 5, 7, ..., т. е. на выходе младшего разряда должна быть 1, если она есть на входе № 1 или на входе № 3 и т. д. Поэтому входы под указанными номерами через элемент ИЛИ соединяются с выходом младшего разряда. Единицу во втором разряде двоичного кода имеют десятичные цифры 2, 3, 6, 7, . . .; входы с этими номерами через элемент ИЛИ должны подключаться к выходу шифратора, на котором устанавливается второй разряд кода. Аналогично, входы 4, 5, 6, 7,... через элемент ИЛИ должны быть соединены с выходом, на котором устанавливается третий разряд, так как их коды имеют в этом разряде единицу, и т. д.

Схема шифратора, построенная в соответствии с изложенным принципом, приведена на рис. 3.9,а, а условное изображение - на рис. 3.9, б, где E - вход разрешения работы, а Е 0 - выход, логический 0 на котором свидетельствует о том, что ни один информационный вход не возбужден. Для расширения разрядности (каскадирования) шифраторов вход E последующего шифратора соединяют с выходом E 0 .предыдущего. Если информационные входы предыдущего шифратора не возбуждены (E 0 =0), то последующий шифратор получает разрешение работать.

Применение шифраторов

Шифратор может быть организован не только для представления (кодирования) десятичного числа двоичным кодом, но и для выдачи определенного кода (его значение заранее выбирается), например, при нажатии клавиши с соответствующим символом. При появлении этого кода система оповещается о том, что нажата определенная клавиша клавиатуры.

Шифраторы применяются в устройствах, преобразующих один вид кода в другой. При этом вначале дешифрируется комбинация исходного кода, в результате чего на соответствующем выходе дешифратора появляется логическая 1. Это отображение входного кода, значение которого определено номером возбужденного выхода дешифратора, подается на шифратор, организованный с таким расчетом, чтобы каждый входной код вызывал появление заданного выходного кода.

Одними из очень важных элементов цифровой техники, а особенно в компьютерах и системах управления являются шифраторы и дешифраторы.

Когда мы слышим слово шифратор или дешифратор, то в голову приходят фразы из шпионских фильмов. Что-то вроде: расшифруйте депешу и зашифруйте ответ.

В этом нет ничего неправильного, так как в шифровальных машинах наших и зарубежных резидентур используются шифраторы и дешифраторы.

Шифраторы.

Таким образом, шифратор (кодер), это электронное устройство, в данном случае микросхема, которая преобразует код одной системы счисления в код другой системы. Наибольшее распространение в электронике получили шифраторы, преобразующие позиционный десятичный код, в параллельный двоичный. Вот так шифратор может обозначаться на принципиальной схеме.

К примеру, представим, что мы держим в руках обыкновенный калькулятор, которым сейчас пользуется любой школьник.

Поскольку все действия в калькуляторе выполняются с двоичными числами (вспомним основы цифровой электроники), то после клавиатуры стоит шифратор, который преобразует вводимые числа в двоичную форму.

Все кнопки калькулятора соединяются с общим проводом и, нажав, к примеру, кнопку 5 на входе шифратора, мы тут же получим двоичную форму данного числа на его выходе.

Конечно же, шифратор калькулятора имеет большее число входов, так как помимо цифр в него нужно ввести ещё какие-то символы арифметических действий, поэтому с выходов шифратора снимаются не только числа в двоичной форме, но и команды.

Если рассмотреть внутреннюю структуру шифратора, то несложно убедиться, что он выполнен на простейших базовых логических элементах .

Во всех устройствах управления, которые работают на двоичной логике, но для удобства оператора имеют десятичную клавиатуру, используются шифраторы.

Дешифраторы.

Дешифраторы относятся к той же группе, только работают с точностью до наоборот. Они преобразуют параллельный двоичный код в позиционный десятичный. Условное графическое обозначение на схеме может быть таким.

Или таким.

Если говорить о дешифраторах более полно, то стоит сказать, что они могут преобразовывать двоичный код в разные системы счисления (десятичную, шестнадцатиричную и пр.). Всё зависит от конкретной цели и назначения микросхемы.

Простейший пример . Вы не раз видели цифровой семисегментный индикатор, например, светодиодный. На нём отображаются десятичные цифры и числа к которым мы привыкли с детства (1, 2, 3, 4...). Но, как известно, цифровая электроника работает с двоичными числами, которые представляют комбинацию 0 и 1. Что же преобразовало двоичный код в десятичный и подало результат на цифровой семисегментный индикатор? Наверное, вы уже догадались, что это сделал дешифратор.

Работу дешифратора можно оценить вживую, если собрать несложную схему, которая состоит из микросхемы-дешифратора К176ИД2 и светодиодного семисегментного индикатора, который ещё называют «восьмёркой». Взгляните на схему, по ней легче разобраться, как работает дешифратор. Для быстрой сборки схемы можно использовать беспаечную макетную плату .

Для справки. Микросхема К176ИД2 разрабатывалась для управления 7-ми сегментным светодиодным индикатором. Эта микросхема способна преобразовать двоичный код от 0000 до 1001 , что соответствует десятичным цифрам от 0 до 9 (одна декада). Остальные, более старшие комбинации просто не отображаются. Выводы C, S, K являются вспомогательными.

У микросхемы К176ИД2 есть четыре входа (1, 2, 4, 8). Их ещё иногда обозначают D0 - D3 . На эти входы подаётся параллельный двоичный код (например, 0001). В данном случае, двоичный код имеет 4 разряда. Микросхема преобразует код так, что на выходах (a - g ) появляются сигналы, которые и формируют на семисегментном индикаторе десятичные цифры и числа, к которым мы привыкли. Так как дешифратор К176ИД2 способен отобразить десятичные цифры в интервале от 0 до 9, то на индикаторе мы увидим только их.

Ко входам дешифратора К176ИД2 подключены 4 тумблера (S1 - S4), с помощью которых на дешифратор можно подать параллельный двоичный код. Например, при замыкании тумблера S1 на 5 вывод микросхемы подаётся логическая единица. Если же разомкнуть контакты тумблера S1 - это будет соответствовать логическому нулю. С помощью тумблеров мы сможем вручную устанавливать на входах микросхемы логическую 1 или 0. Думаю, с этим всё понятно.

На схеме показано, как на входы дешифратора DD1 подан код 0101. На светодиодном индикаторе отобразится цифра 5. Если замкнуть только тумблер S4, то на индикаторе отобразится цифра 8. Чтобы записать число от 0 до 9 в двоичном коде достаточно четырёх разрядов: a 3 * 8 + a 2 * 4 + a 1 * 2 + a 0 * 1 , где a 0 - a 3 , - это цифры из системы счисления (0 или 1).

Представим число 0101 в десятичном виде 0101 = 0*8 + 1*4 + 0*2 + 1*1 = 4 + 1 = 5 . Теперь взглянем на схему и увидим, что вес разряда соответствует цифре, на которую умножается 0 или 1 в формуле.

Дешифратор на базе технологии ТТЛ - К155ИД1 использовался в своё время для управления газоразрядным цифровым индикатором типа ИН8, ИН12, которые были очень востребованы в 70-е годы, так как светодиодные низковольтные индикаторы ещё были очень большой редкостью.

Всё изменилось в 80-е годы. Можно было свободно приобрести семисегментные светодиодные матрицы (индикаторы) и среди радиолюбителей прокатился бум сборки электронных часов. Самодельные электронные часы не собрал для дома только ленивый.

3.1.2 Шифраторы

Шифрирование это способ сжатия данных за счет преобразования m -разрядного унитарного (десятичного) кода в n -разрядный двоичный или двоично-десятичный код (m > n ). Шифраторы (CD , coder ) выполняют функцию, обратную функции дешифратора. При поступлении сигнала на один из входов шифратора на его выходах формируется код, соответствующий номеру этого входа.

Полный шифратор (m – n ) имеет m = 2 n входов и n выходов, если m < 2 n , то шифратор не полный. Также он может быть неприоритетным, если разрешена подача только одного активного сигнала или приоритетным, если допускается подача одновременно нескольких активных сигналов на входы.

Принцип работы полного неприоритетного шифратора (4 – 2) поясняется таблицей истинности (таблица 1).

Таблица истинности неприоритетного шифратора (4 – 2) Таблица 1

|

набора |

Информационные входы |

Выходы |

||||

|

X 3 |

X 2 |

X 1 |

X 0 |

F 1 |

F 0 |

|

Карты Карно для минимизации схемы шифраторов обычно не используются вследствие сложности составления при большом количестве переменных.

Из таблицы (1) следует, что младший разряд F 0 кода на выходе шифратора равен единице, когда на нечетных входах присутствует единица:

Старший разряд

F

1

кода на выходе шифратора равен единице, когда на

входах

X

3

,

X

2

присутствует единица:

Старший разряд

F

1

кода на выходе шифратора равен единице, когда на

входах

X

3

,

X

2

присутствует единица:

Следовательно, схема шифратора (4 – 2) может быть реализована с помощью двух элементов 2ИЛИ (рис. 1, а).

Рис. 1 Схемы неприоритетного шифратора (4 – 2) на элементах 2ИЛИ (а), 2ИЛИ-НЕ (б)

Для инверсной записи (рис. 1, б):

Один из входных сигналов шифратора обязательно имеет единичное значение (таблица 1). Если на входах X 1 , X 2 , X 3 нулевые значения, это означает, ч то на входеX 0 логическая единица, соответствующая набору 0, и этот вход к схеме может быть не подключен (рис. 1, а). Аналогично для X 3 в схеме шифратора на рис. 1, б. Схемы шифраторов на рисунке отличаются зеркальной перестановкой входов (в обоих случаях младший разряд X 0 , старший X 3 ) и инвертированием выходных сигналов (рис.1, б).

У шифраторов обычно имеются служебные входы и выходы:

- Разрешающий (стробирующий) вход EI (EN ) для выбора времени срабатывания шифратора при условии EI =1, также для наращивания разрядности входного кода.

- Разрешающий выход EO (EN ), определяет отсутствие сигналов на всех информационных выходах (EO = 1). Используется для увеличения разрядности путем подключения дополнительных шифраторов, условие подключения EO =1.

- Разрешающий выход GS (CS ), указывает на наличие информационного сигнала хотя бы на одном входе, принимая значение GS = 1. Обеспечивает согласование работы шифратора и внешних устройств (микропроцессор). Может применяться в схеме наращивания разрядности шифратора для исключения ошибок преобразования кодов.

Одно из основных назначений шифратора – ввод данных в цифровые устройства с помощью клавиатуры. Шифраторы, которые при одновременном нажатии нескольких клавиш вырабатывают код только старшей цифры, называют приоритетными. Если эти шифраторы выявляют старшую (левую) единицу и формируют двоичный код соответствующего единице десятичного номера, то называются указателями старшей единицы (обозначение элемента HPR 1/ BIN ).

В таблице истинности указателя старшей единицы (таблица 2) символом «Х» обозначены значения входных переменных, которые не важны для устройства и могут быть равны 0 или 1. Интерес представляют единицы в старшем разряде соответствующего набора.

Символом « – » обозначены значения переменных, которые не поступают в шифратор, т.к. на разрешающем входе EI сигнал логического нуля, на выходе F 1 F 0 = 00.

Пример : если нажата клавиша старшего разряда Х 3 (набор 5), что соответствует кодам 3 10 = 11 2 , нажатие других клавиш должно игнорироваться.

|

Таблица истинности указателя старшей единицы (4 – 2) Таблица 2 |

|||||||||

|

набора |

Служебные |

Информационные |

|||||||

|

вход |

выходы |

Входы |

Выходы |

||||||

|

EI |

GS |

EO |

X 3 |

X 2 |

X 1 |

X 0 |

F 1 |

F 0 |

|

В соответствии с правилом склеивания для выхода F 1 .